- Memory hierarchy

- Store everything on disk

- Copy recently accessed (and nearby) items from disk to smaller DRAM memory

- Main memory

- Copy more recently accessed (and nearby) items from DRAM to smaller SRAM memory

- Cache memory attached to CPU

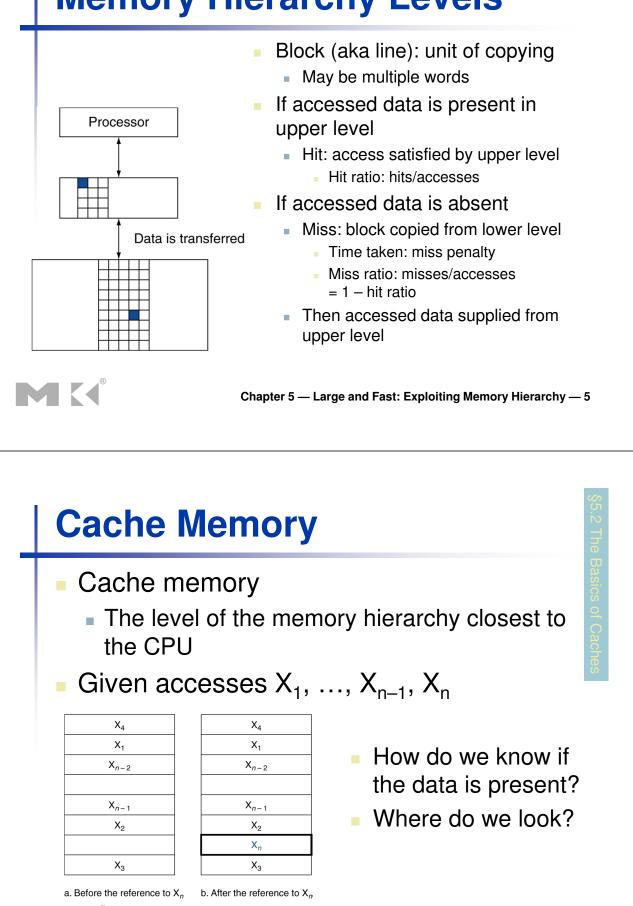

#### **Memory Hierarchy Levels**

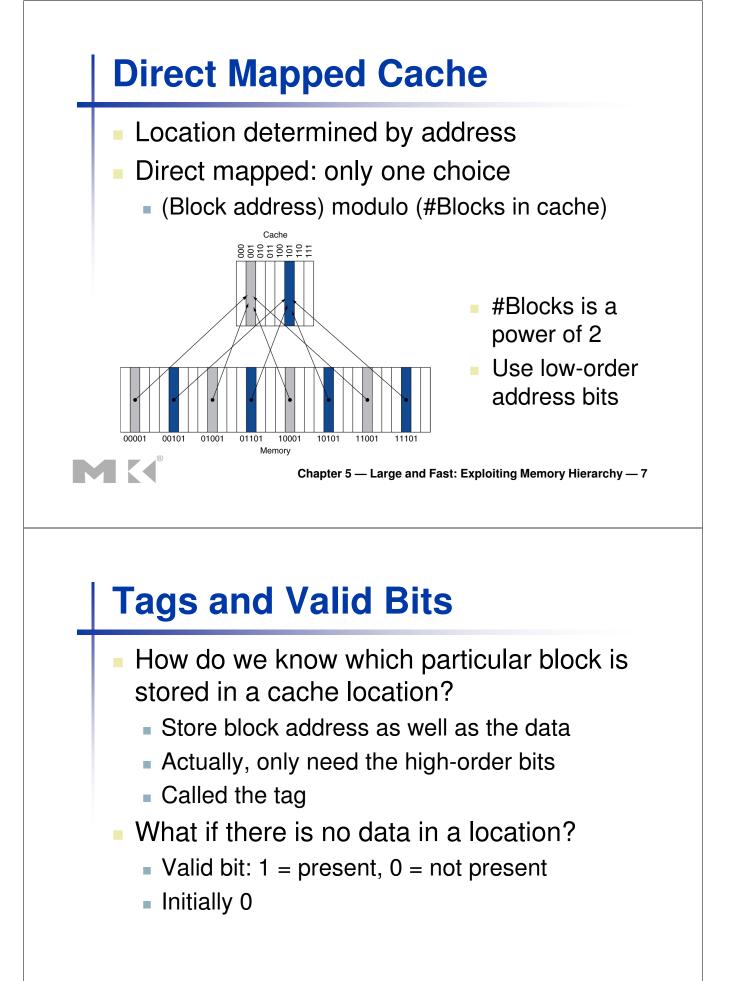

# **Cache Example**

- 8-blocks, 1 word/block, direct mapped

- Initial state

| Index | V | Tag | Data |

|-------|---|-----|------|

| 000   | N |     |      |

| 001   | N |     |      |

| 010   | N |     |      |

| 011   | N |     |      |

| 100   | N |     |      |

| 101   | N |     |      |

| 110   | N |     |      |

| 111   | N |     |      |

# **Cache Example**

| Word addr | Binary addr | Hit/miss | Cache block |

|-----------|-------------|----------|-------------|

| 22        | 22 10 110   |          | 110         |

| Index | V | Tag | Data       |

|-------|---|-----|------------|

| 000   | Ν |     |            |

| 001   | Ν |     |            |

| 010   | N |     |            |

| 011   | N |     |            |

| 100   | N |     |            |

| 101   | N |     |            |

| 110   | Υ | 10  | Mem[10110] |

| 111   | Ν |     |            |

MK

Chapter 5 — Large and Fast: Exploiting Memory Hierarchy — 9

# **Cache Example**

| Word addr | Binary addr | Hit/miss | Cache block |

|-----------|-------------|----------|-------------|

| 26        | 26 11 010   |          | 010         |

| Index | V | Tag | Data       |

|-------|---|-----|------------|

| 000   | Ν |     |            |

| 001   | Ν |     |            |

| 010   | Υ | 11  | Mem[11010] |

| 011   | N |     |            |

| 100   | Ν |     |            |

| 101   | Ν |     |            |

| 110   | Y | 10  | Mem[10110] |

| 111   | Ν |     |            |

Chapter 5 — Large and Fast: Exploiting Memory Hierarchy — 11

#### **Cache Example**

| Word addr | Binary addr | Hit/miss | Cache block |

|-----------|-------------|----------|-------------|

| 22        | 10 110      | Hit      | 110         |

| 26        | 11 010      | Hit      | 010         |

| Index | V | Tag | Data       |

|-------|---|-----|------------|

| 000   | Ν |     |            |

| 001   | N |     |            |

| 010   | Y | 11  | Mem[11010] |

| 011   | N |     |            |

| 100   | N |     |            |

| 101   | N |     |            |

| 110   | Y | 10  | Mem[10110] |

| 111   | Ν |     |            |

# **Cache Example**

| Word  | oddr      | Binanya | ddr         | Hit/miss | Cache block |

|-------|-----------|---------|-------------|----------|-------------|

| woru  | Word addr |         | Binary addr |          |             |

| 16    | 16        |         | 10 000      |          | 000         |

| 3     | 3         |         | 00 011      |          | 011         |

| 16    | 16        |         | 10 000      |          | 000         |

| Index | V         | Tag     | Dat         | a        |             |

| 000   | Υ         | 10      | Me          | m[10000] |             |

| 001   | N         |         |             |          |             |

| 010   | Y         | 11      | Mem[11010]  |          |             |

| 011   | Υ         | 00      | Me          | m[00011] |             |

| 100   | Ν         |         |             |          |             |

| 101   | Ν         |         |             |          |             |

| 110   | Y         | 10      | Me          | m[10110] |             |

| 111   | Ν         |         |             |          |             |

Chapter 5 — Large and Fast: Exploiting Memory Hierarchy — 13

# **Cache Example**

| Word addr | Binary addr | Hit/miss | Cache block |

|-----------|-------------|----------|-------------|

| 18        | 18 10 010   |          | 010         |

| Index | V | Tag | Data       |

|-------|---|-----|------------|

| 000   | Y | 10  | Mem[10000] |

| 001   | N |     |            |

| 010   | Υ | 10  | Mem[10010] |

| 011   | Y | 00  | Mem[00011] |

| 100   | N |     |            |

| 101   | N |     |            |

| 110   | Y | 10  | Mem[10110] |

| 111   | Ν |     |            |

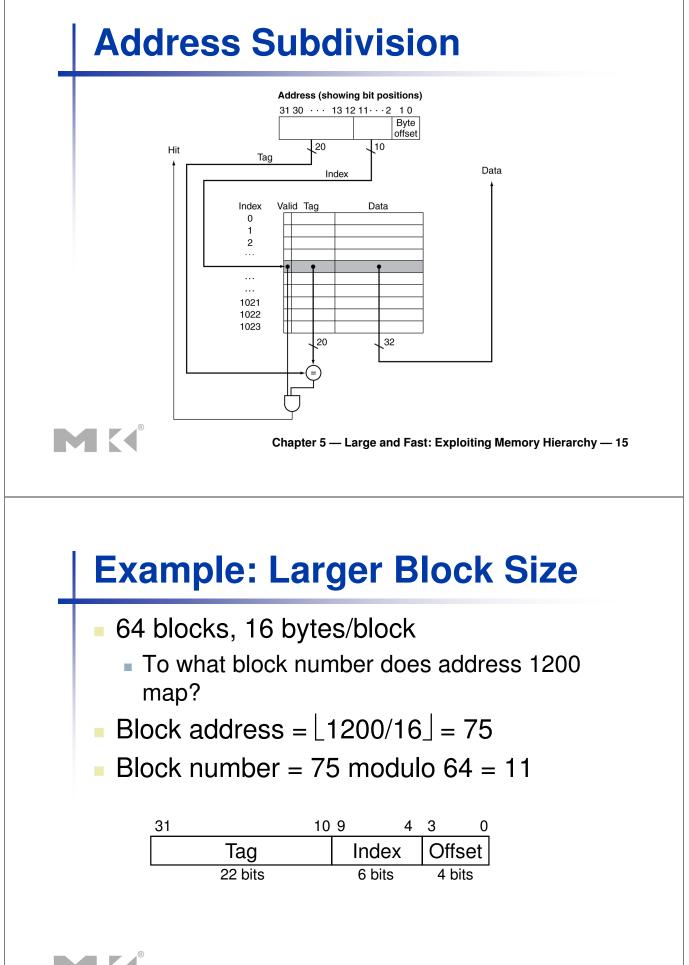

# **Block Size Considerations**

- Larger blocks should reduce miss rate

- Due to spatial locality

- But in a fixed-sized cache

- Larger blocks ⇒ fewer of them

- More competition  $\Rightarrow$  increased miss rate

- Larger blocks  $\Rightarrow$  pollution

- Larger miss penalty

- Can override benefit of reduced miss rate

- Early restart and critical-word-first can help

Chapter 5 — Large and Fast: Exploiting Memory Hierarchy — 17

# **Cache Misses**

- On cache hit, CPU proceeds normally

- On cache miss

- Stall the CPU pipeline

- Fetch block from next level of hierarchy

- Instruction cache miss

- Restart instruction fetch

- Data cache miss

- Complete data access

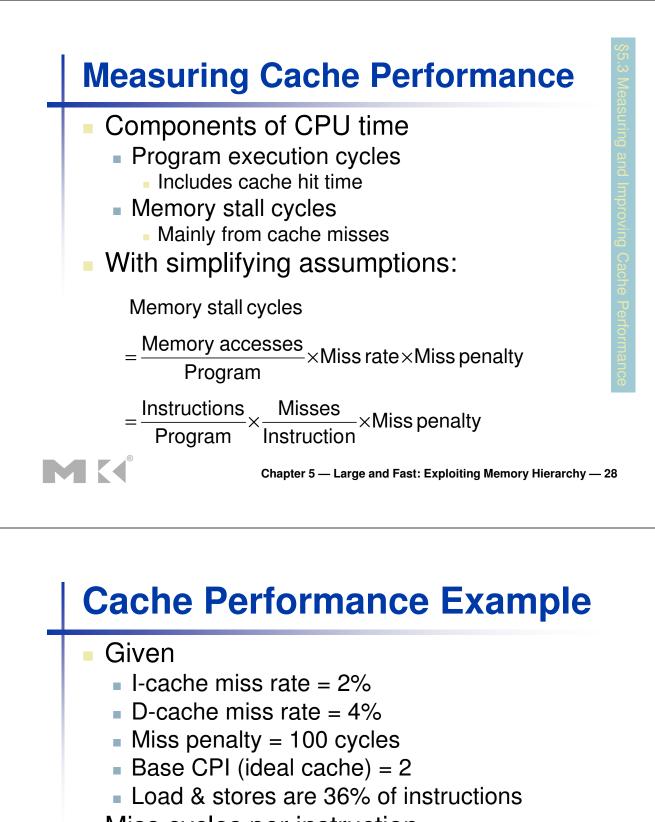

- Miss cycles per instruction

- I-cache: 0.02 × 100 = 2

- D-cache: 0.36 × 0.04 × 100 = 1.44

- Actual CPI = 2 + 2 + 1.44 = 5.44

- Ideal CPU is 5.44/2 =2.72 times faster